# CMOS-Compatible Catalyst for MacEtch: Titanium Nitride-Assisted Chemical Etching in Vapor phase for High Aspect Ratio Silicon Nanostructures

Jeong Dong Kim, †, Munho Kim, †, localization Clarence Chan, Nerissa Draeger, James J. Coleman, Samuel Coleman and Xiuling Li\*,†0

Supporting Information

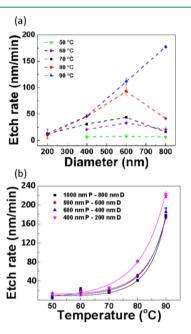

ABSTRACT: Metal-assisted chemical etching (MacEtch) is an emerging anisotropic chemical etching technique that has been used to fabricate high aspect ratio semiconductor micro- and nanostructures. Despite its advantages in unparalleled anisotropy, simplicity, versatility, and damage-free nature, the adaptation of MacEtch for silicon (Si)-based electronic device fabrication process is hindered by the use of a gold (Au)-based metal catalyst, as Au is a detrimental deep-level impurity in Si. In this report, for the first time, we demonstrate CMOS-compatible titanium nitride (TiN)-based MacEtch of Si by establishing a true vapor-phase (VP) MacEtch approach in order to overcome TiN-MacEtch-specific challenges. Whereas inverse-MacEtch is observed using conventional liquid phase MacEtch because of the limited mass transport from the strong adhesion between TiN and Si, the true VP etch leads to forward MacEtch and produces Si nanowire arrays by engraving the TiN mesh pattern in Si. The etch rate as a function of etch temperature, solution concentration, TiN dimension, and thickness is systematically characterized to uncover the

underlying nature of MacEtching using this new catalyst. VP MacEtch represents a significant step toward scalability of this disruptive technology because of the high controllability of gas phase reaction dynamics. TiN-MacEtch may also have direct implications in embedded TiN-based plasmonic semiconductor structures for photonic applications.

KEYWORDS: Titanium nitride, CMOS-compatible, metal-assisted chemical etching, vapor-phase MacEtch, silicon, nanowire

## **■** INTRODUCTION

Metal-assisted chemical etching (MacEtch) is a local electrochemical etching method capable of producing anisotropic high aspect ratio semiconductor structures with a simple wet etching process catalyzed by a patterned metal film. 1-3 MacEtch eliminates high-energy ion-induced damage and sidewall scallops that typically occur in conventional deep reactive ion etching.<sup>4</sup> Nanowires (NW), vias, trenches, and other surface textures have been demonstrated using MacEtch for silicon (Si), germanium (Ge), and compound semiconductors (GaAs, InGaAs, InP, GaP, GaN,  $\beta$ -Ga<sub>2</sub>O<sub>3</sub>), either in the forward or inverse manner relative to the catalyst location.5-10 They have been used as the building blocks in electronic and optoelectronic device applications such as lightemitting diodes, solar cells, photodetectors, biosensors, super capacitors, thermo-electrics, and FinFETs. 8,9,11-16

Typical Si MacEtch starts by depositing a noble metal catalyst film such as gold (Au), platinum (Pt), or silver (Ag) on the semiconductor surface. The catalyst can be patterned into any arbitrary geometry by a variety of lithography or nonlithographical methods. Then, the sample is immersed in a solution mixture of n acid (e.g., hydrofluoric acid (HF)) and an oxidant (e.g., hydrogen peroxide (H<sub>2</sub>O<sub>2</sub>)) to selectively oxidize and dissolve the semiconductor localized under the catalyst. 1-3 During MacEtch, at the liquid-catalyst interface, electronic holes are produced by the reduction reaction of the oxidant (cathodic reaction), which are injected in the valence band to produce oxidized semiconductor (anodic reaction) that is subsequently dissolved by the acid. The process of electronic holes generated and injected into the semiconductor is defined as the carrier generation step and the transport of the etchant and byproducts is defined as the mass transport step.<sup>17</sup> The etch rate is affected by both the carrier generation and mass transport steps: in the carrier generation-dominant

Received: February 8, 2019 Accepted: July 2, 2019 Published: July 2, 2019

<sup>&</sup>lt;sup>†</sup>Department of Electrical and Computer Engineering, Micro and Nanotechnology Laboratory, University of Illinois at Urbana-Champaign, Champaign, Illinois 61801, United States

<sup>&</sup>lt;sup>‡</sup>Lam Research Corporation, Fremont, California 94538, United States

Spepartment of Electrical Engineering and Department of Materials Science, University of Texas at Dallas, Richardson, Texas 75080, United States

regime, the etch rate is governed by the amount of the holes injected in the semiconductor, and in the mass transport dominant regime, it is governed by how fast the oxidized semiconductor can be removed so that the next pristine semiconductor surface is exposed for the next oxidation cycle to start. Because of the material dissolution taking place laterally underneath the catalyst surface, the mass transport rate is influenced by the size of catalyst and the van der Waals force between the catalyst and semiconductor. 18-20 On the other hand, carrier generation is affected by the electrochemical potential of the oxidant and the metal catalyst, 16 and the metal-semiconductor barrier height that is defined by the band gap, electron affinity, and doping concentration of the semiconductor and metal work function. 10,21 Noble metals of Au, Ag, Pt, Pd, Cu have been reported as MacEtch catalysts<sup>3</sup> and showed that the etch rate and porosity can be engineered by using metals with different electrochemical potentials.

Despite its simplicity of producing high aspect ratio complex semiconductor structures, using noble metal catalyst, especially Au, is the major limitation for MacEtch to be applied in electronic device applications specifically in the front end of the line (FEOL) and back end of the line (BEOL) in the complementary metal-oxide semiconductor (CMOS) fabrication process because of the deep-level defects concern.<sup>22</sup> In order for MacEtch to be applied in the CMOS process, the catalyst not only has to be CMOS-compatible but also has to satisfy the MacEtch catalyst requirements of hole generation and injection capability, as well as high HF chemical resistivity. Recently, nonconventional metal material with high conductivity has been investigated as the MacEtch catalyst. Graphene-assisted chemical etching (GaCE) was demonstrated by Kim et al. in 2013.<sup>23</sup> The authors patterned the transferred graphene on a Si substrate using anodic aluminum oxides as the patterning templates, then, etched the sample in HF and H<sub>2</sub>O<sub>2</sub> at temperatures of 40-50 °C to form nanopillar arrays with a aspect ratio as high as ~6:1. However, GaCE is sensitive to the structural nonuniformity of graphene resulted from the grain boundaries and point defects such that the uniformity of the nanopillar array across the graphene mesh formed by GaCE was poor. In addition, any Cu residue from the wet or dry transfer can lead to the formation of deep-level defects. Therefore, the GaCE using transferred graphene is still not CMOS-compatible at this stage.

In this work, for the first time, we present a fully CMOScompatible MacEtch demonstration using titanium nitride (TiN) as the catalyst. TiN is a particularly attractive material because of its CMOS compatibility. TiN has been used as a diffusion barrier or electromigration blocking layer for metal interconnects in modern integrated circuits, because of its low resistivity, high thermal stability, mechanical durability, and excellent step coverage.<sup>24</sup> TiN is chemically resistive to HF,<sup>25,26</sup> has a electrochemical potential between 0.5 and 0.9 V,<sup>27</sup> and a work function of 4.5 eV;<sup>28</sup> thus, it is suitable to serve as a MacEtch catalyst. However, the adhesion and Young's modulus of TiN on Si is known to be much stronger than Au on Si, 29 resulting in distinctly different etching behavior compared to Au-MacEtch. van der Waals force is one of the dominant sources of attraction between Si and the catalyst. 18,19 After each cycle of carrier generation and mass transport reactions, the catalyst adheres to the semiconductor surface by the van der Waals force. 18 In the case of TiN-Si, because of the strong adhesion at the interface, it is difficult for the mass transport reaction to take place laterally underneath the

catalyst. In addition, the catalyst cannot be easily conformal to the etched topography of the surface because of the large Young's modulus, reducing the efficiency of charge transport. Both of these trends tend to favor inverse MacEtch (I-MacEtch).8,9,16

We first show the I-MacEtch behavior using a conventional liquid phase (LP) MacEtch, presumably because of limited mass transport at the interface between TiN and Si. We then attempted a pseudo-vapor-phase (VP) MacEtch method, slightly modified from the one pioneered by Hildredth et al.30 aiming to enhance mass transport, which leads to partial forward MacEtch while mostly still dominated by the I-MacEtch behavior. We finally developed a true-VP MacEtch approach, which enabled the fabrication of ordered Si NW arrays with aspect ratio of >5:1 from a TiN mesh-patterned Si wafer. The etch depth as a function of patterned TiN mesh dimension, solution concentration, etching temperature, and TiN film thickness are systematically investigated to characterize and understand the etching behavior of this new catalyst.

#### ■ RESULTS AND DISCUSSION

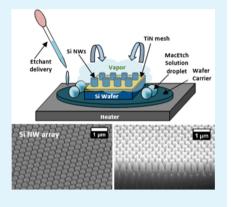

TiN I-MacEtch under LP-MacEtch. Compared to Au-MacEtch, the etch rate using TiN as the catalyst is much slower and little etching was observed at room temperature within the process window experimented. All etching results presented below were obtained at elevated temperatures from 50 to 90 °C. Figure 1a shows the conventional LP MacEtch setup schematic and the resulted morphology of a Si wafer covered with a TiN mesh pattern after LP-MacEtching in a solution of 0.28 M HF, 13 mM H<sub>2</sub>O<sub>2</sub>, 0.39 M IPA for 30 min at 70 °C. It can be seen that the exposed Si area in the mesh holes has been etched whereas the Si directly underneath the TiN mesh catalyst remains intact, resulting in the periodic hole array surface textures and revealing the I-MacEtch nature. The I-MacEtch process can also be clearly seen in the crosssectional scanning electron microscopy (SEM) image of a 5 min LP-MacEtched sample shown in Figure S1 in the Supporting Information. Note that no etching takes place without the presence of TiN, confirming the catalytic nature of TiN for this etching reaction.

It is well known that I-MacEtch results from limited mass transport of the etchant under the metal catalyst. 8-10,31 Under I-MacEtch, the generation of electronic holes from the oxidant at the catalyst surface is faster than the removal of the oxidized Si formed under the catalyst; thus the unconsumed holes localized at the catalyst attract the electrons in areas in between the catalyst, leaving the Si in that region oxidized instead. In the case of the TiN-Si interface, it is known that the adhesion between the two surfaces is extremely strong, <sup>29</sup> so it is highly likely that the etchant has a difficult time to penetrate the interface for etching to continue. Therefore, it is not surprising that TiN catalyzed etching shows I-MacEtch.

Pseudo-VP-MacEtch. In an effort to enhance the mass transport of etchants, we attempted to use a VP etching setup illustrated in Figure 1b, slightly modified from the one pioneered by Hildreth et al. for the demonstration of MacEtch using Au, Ag, Pd/Au catalysts on Si substrates.<sup>30</sup> In this case, the TiN patterned sample was held upside down ~5 cm above the MacEtch solution. The solution was heated while the substrate was kept at room temperature. The MacEtch takes place when the solution is evaporated and diffused onto the sample surface. The SEM image shows the resulted etching morphology using this setup for an otherwise identical sample **ACS Applied Materials & Interfaces**

Figure 1. Schematic illustrations of three kinds of MacEtch setups and the corresponding etching morphology of TiN mesh patterned Si substrate shown in 45° tilted SEM images: (a) conventional LP-MacEtch, where the TiN patterned silicon (Si) sample is immersed in solution during etching; Si is preferentially etched inside the TiN mesh holes, leaving behind an indented periodic structure, indicating the I-MacEtch nature. (b) Pseudo-VP MacEtch, where the TiN patterned sample faces down and is separated by a gap from the solution; the material at the edge of the mesh holes are preferentially removed but the center area remains intact, forming periodic pyramids as a result of partial I-MacEtch. (c) True VP-MacEtch, where the TiN patterned Si sample faces up, and the vapor etchant is provided by the solution droplets placed on a heated dummy wafer carrier; materials in the mesh holes are intact whereas areas underneath the mesh are removed, demonstrating successful forward MacEtch.

and etch condition as in Figure 1a, except for only 5 min. The morphology is clearly different from that using the conventional LP-MacEtch in Figure 1a. However, in contrast to 100% forward MacEtch as in the case of Au-catalyzed Si MacEtch,<sup>30</sup> it only resulted in partial forward and partial I-MacEtch: pyramid-shaped pillars with clear facets are formed in the exposed Si (TiN mesh hole) region, whereas the TiN mesh covered region also got etched into ridges. This indicates that this kind of VP-MacEtch is indeed enhancing the mass transport to reduce the inverse etching effect (the center of the mesh hole area remains not etched), but still not sufficient to completely quench the I-MacEtch. We attribute this etching phenomenon to the simultaneous MacEtch reactions in vapor and LPs, because in this setup (Figure 1b), the vapor generated from the heated solution is easily condensed onto the nonheated sample surface, which blocks the mass transport path of the vapor etchant and byproduct species. This method will be denoted as pseudo-VP MacEtch from here on.

**True VP-MacEtch.** In order to overcome the vapor condensation issue, both the solution and the sample must be heated, ideally at the same temperature. Figure 1c shows the schematic of the modified VP-MacEtch setup and resulted etch morphology of an identical sample and etch condition as in

Figure 1b. A dummy 4 in. Si substrate is placed on the hot plate and the TiN mesh-patterned Si sample is placed on top of the heated dummy substrate. Droplets (10  $\mu$ L) from the premixed MacEtch solution were dispersed on the dummy Si substrate ~1 cm away from the edge of the TiN patterned sample using the micro-pipette. The MacEtch starts when the vaporized MacEtch solution diffuses onto the TiN sample. The solution droplets on the dummy wafer were replenished right after the droplets were completely evaporated. As can be seen from the SEM image, the Si under the TiN mesh is uniformly etched leaving behind flat top pillars in the mesh hole region, demonstrating successful forward MacEtch process using TiN catalyst.

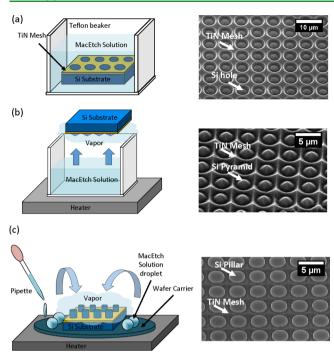

Figure 2a-d shows 52° tilted FIB cross-sectional SEM images showing the resulted etch morphology of VP-MacEtch

Figure 2. 52° tilted cross-sectional SEM images after FIB, showing the NW array fabricated by true VP-MacEtch with the TiN catalyst mesh pattern hole size of (a) 800 nm diameter, 1 µm pitch (b) 600 nm diameter, 800 nm pitch, (c) 400 nm diameter, 600 nm pitch, and (d) 200 nm diameter, 400 nm pitch.

with the TiN mesh pattern diameter of 800, 600, 400, and 200 nm at fixed spacing of 200 nm in a solution of 0.28 M HF, 13 mM H<sub>2</sub>O<sub>2</sub>, 0.39 M IPA at 90 °C for 5 min. Si under the TiN etches down vertically producing the uniform near-vertical (80°) NW arrays. An aspect ratio of >5:1 is achieved in the 200 nm diameter. Much higher aspect ratio is expected with longer etch time. The rough top surface and slight tapering of the sidewalls of the etched pillars are a result of the etching resulted from diffusion of the unconsumed holes from the TiN pads.

We attribute the well-defined forward MacEtch to the new setup, which enabled the effective VP diffusion of the reactants (HF and H<sub>2</sub>O<sub>2</sub>) and the etching byproducts (H<sub>2</sub>O, H<sub>2</sub>SiF<sub>6</sub>, and H2), to ensure continuous cycles of catalyzed oxidation and lateral removal of the oxide at the tight interface of the unique TiN metal catalyst and Si. As in LP-MacEtch, the etch rate is directly affected by the transport of the etchant and byproducts. Importantly, the diffusion in the VP is related to the temperature with order of 3/2 according to the Chapman-Enskog theory,<sup>32</sup> where in LP, the diffusion coefficient of the solution is affected by the dynamic viscosity of the solution linearly according to the Stokes-Einstein equation.<sup>33</sup> Therefore, the mass transport can be significantly enhanced in the VP-MacEtch to overcome the limited mass transport resulted from the strong van der Waals force between TiN and the Si substrate.<sup>29</sup> Note that the liquid byproducts (H<sub>2</sub>O<sub>2</sub> and H<sub>2</sub>SiF<sub>6</sub>) need to be evaporated to be diffused to atmosphere whereas the vapor byproducts  $(H_2, SiF_6)$  can be diffused as they are produced. When the evaporation rate of the liquid byproducts is slow because of the low substrate temperature, the vapor byproducts can be trapped under the catalyst, which can lead to the delamination or crack of the TiN catalyst film.

Etch Rate Dependence and Activation Energy. We have reported previously<sup>34</sup> etch rate dependence on catalyst mesh diameters and pitch systematically for Au-catalyzed MacEtch previously, confirming the competition between carrier generation and mass transport during the etch process. A similar trend is observed here for TiN-MacEtch, as shown in Figure S2. To explore the temperature-dependent etch rate behavior for TiN-MacEtch, Figure 3a plots the average etch

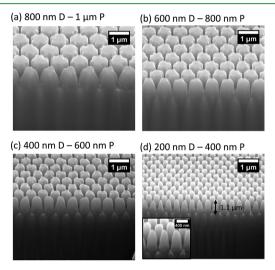

Figure 3. Average etch rate of the NWs using VP-MacEtch with a fixed solution concentration of 0.28 M HF, 13 mM H<sub>2</sub>O<sub>2</sub>, 0.39 M IPA for 5 min, plotted as a function of (a) TiN mesh pattern hole diameter from 200 to 800 nm at a fixed pitch of 1  $\mu m$  under varied etching temperatures from 50 to 90 °C as labeled and (b) etching temperature at a fixed mesh hole spacing of 100 nm but varied diameter (D) and pitch (P) as labeled.

rate of the NW as a function of the TiN catalyst mesh diameter from 200 to 800 nm at a fixed pitch of 1000 nm VP-MacEtched in a solution of 0.28 M HF, 13 mM H<sub>2</sub>O<sub>2</sub>, 0.39 M IPA at varied etching temperatures from 50 to 90 °C for 5 min. At 50 °C, the average NW length stays constant at ~30 nm when the diameter increases from 400 to 800 nm. As the temperature increases from 50 to 80 °C, the parabola-like NW length trend appears; 34 at 80 °C, the NW length increases from 50 to 460 nm as the diameter increases from 200 to 600 nm and decreases to 210 nm as the diameter further increases to 800 nm. For 60 to 80  $^{\circ}$ C, the NW length peaks at 600 nm diameter. When the temperature further increases to 90 °C, the NW length continues to increase even when the mesh diameter increases to 800 nm. However, the NW length only increases for diameter from 600 to 800 nm, whereas at the diameter from 200 to 400 nm, the NW lengths are the same as

the corresponding ones in 80 °C. The temperature-dependent etch rate trend from 50 to 80 °C can be divided into three regions: the first region is the smallest diameter examined (200 nm) where the etch rate stays constant at a value of  $60 \pm 9$  nm with increasing temperature. We attribute the constant etch rate to be resulting from the limited mass transport because of the large TiN covered space between the small mesh hole (recall that the pitch is fixed). The oxidized Si removal rate enhanced by increasing temperature in this range is insufficient to increase the vertical etching rate. The second region is the middle diameter range (400-600 nm) where the etch rate increases with increasing temperature and increasing diameter. This is because of the balanced carrier generation (oxidation, which increases with diameter) and mass transport (removal, which increases with temperature). The development of the parabola peak (i.e., maximized NW length) at 600 nm diameter indicates that formation of oxidized Si by carrier generation and removal of the oxidized Si by mass transport are both at maximum. The third region is the large diameter range examined (600-800 nm) where the etch rate increases with temperature but decreases with increasing diameter (except at the highest temperature), attributed to the limited carrier generation rate mechanism, leading to the ultimate parabolic rate curve. This is because the amount of holes injected by the carrier generation is reduced by the increased catalyst mesh hole diameter (decrease in TiN area), whereas the oxidized Si removal rate by mass transport is maximized by increasing temperature. The transition from the parabola to linear etching trend at 90 °C not only supports the enhanced carrier generation at 800 nm diameter but also indicates the saturation of the mass transport enhancement with increasing temperature. It can be imagined that if the TiN mesh hole diameter continued to increase, the curve at 90 °C would make a down turn eventually and transition to parabola shape.

Figure 3b shows the average etch rate of the NW as the function of etching temperature from 50 to 90 °C for fixed spacing of 100 nm but varied pitch of 400, 600, 800, 1000 nm. It can be seen that the etch rate exponentially increases with increasing temperature. The activation energy of the TiN VP-MacEtch can be calculated by fitting the experimental data to Arrhenius equation as shown in eq 1

$$K = A \times e^{-E_a/(K_B T)} \tag{1}$$

where K is the etch rate, A is the frequency factor,  $E_a$  is the activation energy in eV,  $K_B$  is the Boltzmann constant, and T is the temperature in K. An activation energy of 0.78 eV is extracted. This indicates that the energy barrier required for TiN to enable forward MacEtch is higher than that for Au catalyzed MacEtch.5

Etch Rate Dependence on TiN Thickness. Figure 4a shows the etch rate as a function of TiN mesh diameter from 200 to 800 nm at a fixed pitch of 1  $\mu$ m for TiN thickness of 5, 10, and 30 nm VP-MacEtched in a solution of 0.28 M HF, 13 mM H<sub>2</sub>O<sub>2</sub>, and 0.39 M IPA at 80 °C for 5 min. For 5 nm thick TiN, the etch rate decreases gradually from 55 to 12 nm/min as the TiN mesh diameter increases from 400 to 800 nm. As the TiN thickness increases to 10 nm, etch rate increases and the parabola-like dependence on diameter appears with the peak at 600 nm diameter. As the TiN thickness increases to 30 nm, the etch rate for all diameters further increases and the parabola-like trend is clearly shown. Note that the data points for the diameter smaller than 400 nm for 5 and 10 nm thick TiN are missing because the TiN mesh was cracked or **ACS Applied Materials & Interfaces**

Figure 4. (a) Average etch rate of the NWs as a function of TiN mesh hole size from 200 to 800 nm in diameter at a fixed pitch of 1  $\mu$ m but varied TiN thickness of 5, 10, and 30 nm, VP-MacEtched with a fixed solution concentration of 0.28 M HF, 13 mM H<sub>2</sub>O<sub>2</sub>, 0.39 M IPA at 80 °C for 5 min, (b) current density as a function of applied voltage for 10 and 30 nm thick TiN on p-Si.

delaminated for those samples. One of the hypotheses is that the increase in etch rate with increasing TiN thickness is related to the change in Schottky barrier height (SBH). Figure 4b plots, on a double-log scale, the measured current density using interdigitated finger pads as a function of the bias voltage from 0 to 0.6 V for 10 and 30 nm thick TiN film on the same p-Si plain substrate. The current density increases as the TiN thickness increases from 10 to 30 nm. This can be attributed to the decrease in SBH,35 because of the decrease of the work function with the increase in TiN thickness.<sup>36</sup> For our case, the extracted SBHs of 30 and 10 nm TiN from the I-V curves are 0.492 and 0.51 eV, respectively (the SBH extraction details can be found in the Supporting Information). This is consistent with the etch rate variation with TiN thickness observed, because the lowering of SBH with the increase of the TiN thickness makes the hole injection rate to Si higher, thus the etch rate faster. However, it is possible that other factors including the adhesion difference as a result of TiN thickness at the TiN-Si interface play a role on the etch rate also.

We note that it is important to understand the role of the heterojunction between the metal catalyst and the semiconductor in MacEtch. Such studies have been carried out previously by several groups including ours.<sup>3,10,21</sup> The barrier height and band alignment between TiN and Si will change as a function of doping concentration, which will lead to change of the carrier confinement at the interface and the balance of charge and mass transport. The balance of charge and mass transport will obviously also vary as a function of the catalyst pattern and dimension, solution concentration, etching temperature, and TiN thickness. They will in turn change the etch rate and localization, and hence morphology. In this case, TiN forms an Schottky contact with p-Si and the band diagram is illustrated in Figure S11. Because of the low SBHs here, the injected holes are not completely trapped at the

interface. In general, porosity occurs if the SBH is not high enough to confine the carriers where they are generated. 10,377 Although not the focus of this paper, the formation of porous morphology was observed, especially increased as the pillar diameter decreases at a fixed pitch, as shown in Figures S2-S9, because of the oversupply of carriers under limited mass transport condition. By enhancing the mass transport and/or reducing the carrier generation rate, through optimizing the HF to H<sub>2</sub>O<sub>2</sub> concentration ratio (Figure S12) as a function the TiN pattern, thickness, and Si doping levels, the porosity can be minimized. It is also possible to remove the porosity by post-MacEtch digital etching as previously demonstrated for InGaAs.<sup>10</sup> Note that even if it has some porosity, CMOScompatible catalyst enabled MacEtch can still be used for gate poly etch or any other silicon-related etching process as long as it does not impact the CMOS interface. Nonetheless, for future studies, a dedicated VP-MacEtch setup that allows programmable control of the flow of individual etchant, sample temperature, and chamber pressure will be used for systematic mapping of a much bigger parameter space than reported here to scale the etch rate and aspect ratio, as well as porosity.

#### **CONCLUSIONS**

We have demonstrated CMOS-compatible TiN-assisted chemical Etching of Si. We have found that the mass transport in TiN-Si MacEtch is strongly limited as compared to the conventional Au-Si MacEtch under the same etch condition, presumably because of the stronger adhesion property of TiN to Si. Under conventional LP MacEtch condition, areas in the TiN mesh holes are chemically etched producing the I-MacEtched structures. The pseudo-VP-MacEtch resulted in partial forward MacEtch because of vapor condensation on the sample surface by the temperature difference between the substrate and solution vapor. Using the true VP-MacEtch scheme reported here by fixing the substrate and vapor temperature the same, the transition from inverse to forward MacEtch is completed via total VP reaction. The vertical etch rate as a function of TiN mesh dimension, H<sub>2</sub>O<sub>2</sub> concentration, etching temperature, and TiN thickness are systematically characterized with the true VP-MacEtch, confirming the MacEtch mechanism dictated by the carrier generation and mass transport processes. Si NW arrays with aspect ratio >5:1 is realized. The demonstration of producing high aspect ratio Si structures with TiN catalyst shows that MacEtch is not limited to non-CMOS-compatible noble metals and this allows MacEtch to be applied in device applications that are sensitive to deep-level defects. In addition, TiN-MacEtch demonstrated here, which leaves the TiN film embedded in the surface of 3D Si structures, may also have direct implications in TiN-based plasmonic semiconductor structures for photonic applications. 39,40

In summary, this work represents a significant first step toward taking the disruptive MacEtch technique to CMOScompatible commercial applications. Furthermore, transforming solution based MacEtch to VP MacEtch while maintaining the damage free nature holds great potential to controllability and scalability for manufacturing.

## EXPERIMENTAL SECTION

Boron-doped p-Si single crystal (100) substrates with resistivity of 1- $100 \Omega$  cm were used for all experiments. After native oxide etching in 1:100 HF/DI for 60 s, the substrates were deposited with 5, 10, 30 nm TiN using physical vapor deposition by Lam Research Corporation (LRCX). Then, 15 nm  ${\rm SiO_2}$  hard mask was deposited using PECVD (Trion Minilock—Orion PECVD system). Electron beam resist of 950 k poly(methyl methacrylate) (PMMA) in 2% anisole was spin-coated at 2000 rpm for 60 s (~80 nm thickness) and baked at 200 °C for 2 min. Patterns consist of hexagonal ordered dot arrays with diameters varying from 200, 400, 800 nm at pitches of 400, 600, 800, 1000 nm were exposed using electron beam lithography and developed in 1:3 MIBK/IPA for 2 min.

The patterns were transferred on the  $SiO_2$  hard mask by etching in 1:10 buffered oxide etchant (BOE) for 15 s. The PMMA was removed in 5 min cycles in aceton, methanol, and IPA. Then, the residual PMMA was etched by  $O_2$  RIE at 200 mw for 2 min. The exposed TiN patterns were etched in 1:10 NH<sub>4</sub>OH/H<sub>2</sub>O<sub>2</sub> (~15 nm/min). The  $SiO_2$  hard mask was etched in 1:10 BOE for 15 s.

The VP-MacEtch was carried out after the sample patterning. First, a 4 in. dummy Si substrate was placed on the hot plate to serve as a wafer carrier. Then, the TiN patterned Si sample was placed on the center of the wafer carrier. The surface temperature of the wafer carrier and the TiN patterned Si sample were calibrated to match the etching temperature (50, 60, 70, 80, 90 °C). The maximum temperature of 90 °C was chosen only based on the limitation from the experimental setup used, where the MacEtch solution was dispensed onto the wafer carrier manually. At >90 °C, the MacEtch solution evaporated immediately such that it made it difficult to control the continuous generation of vapor around the sample. The MacEtch solution of 0.28 M HF, 13 mM H<sub>2</sub>O<sub>2</sub>, 0.39 M IPA was mixed. The 10  $\mu$ L solution was dropped on the wafer carrier around the TiN patterned Si sample using an HF-resistive micro-pipette. A total of 6-8 pipettes of solutions were dropped on the carrier ~2 cm away from the TiN patterned Si sample. The solution was replenished soon after the drops were completely evaporated. Five samples were etched for each given condition. The VP-MacEtched samples were inspected using a secondary electron microscope (SEM, Hitachi S-4800). No degradation of the TiN mask was observed under all etching conditions for the duration specified. The average NW heights were measured from the 45° tilted SEM images. The height and aspect ratio NWs at the given etching time were inspected by the 52° tilted images after the cross-sectional ion milling using the focused ion beam (FEI-DB4800).

For the current density measurement sample, 15 nm SiO $_2$  by PECVD was deposited onto the same p-Si substrates with 5, 10, and 30 nm thick TiN used for etching. Then, hexamethyldisilane and PR were spin-coated at 4500 rpm for 30 s, respectively, followed by baking at 110 °C for 1 min. An interdigitated pad pattern, with the electrode fingers of 8  $\mu$ m in width, 26  $\mu$ m in spacing, and 290  $\mu$ m in length, was exposed using Karl Suss MJB-3 aligner at 270 mW for 1 min and developed in AZ 917 MIF developer for 2 min. The pattern was then transferred onto SiO $_2$  by etching in BOE for 15 s. After removing PR in acetone, methanol, IPA cycles, the pattern on the SiO $_2$  was transferred onto TiN by etching in 1:10 NH $_4$ OH/H $_2$ O $_2$ . Then, I-V curves were measured using Keithley 4200 parameter analyzer and the current density was calculated by dividing the measured current by the area of the TiN interdigitated pads.

### ASSOCIATED CONTENT

## Supporting Information

The Supporting Information is available free of charge on the ACS Publications website at DOI: 10.1021/acsami.9b00871.

I-MacEtch of the TiN sample in the conventional LP MacEtch; SEM images of VP MacEtched NWs as a function of mesh dimension, solution concentration, etching temperature, and TiN thickness; Schottky barrier height extraction of 30 and 10 nm TiN on Si; band diagram of TiN and p-type Si junction; and tunability of porosity: effect of  $\rm H_2O_2$  concentration on the porosity of Si nanostructures (PDF)

#### AUTHOR INFORMATION

## **Corresponding Author**

\*E-mail: xiuling@illinois.edu.

ORCID ®

Munho Kim: 0000-0002-0379-1886 Xiuling Li: 0000-0003-3698-5182

#### **Present Address**

School of Electrical and Electronic Engineering, Nanyang Technological University, 50 Nanyang Avenue, 639798 Singapore, Singapore.

## **Author Contributions**

<sup>1</sup>J.D.K. and M.K. contributed equally to this work.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This material is based upon work supported by the National Science Foundation under grant nos. 14-62946 and 18-09946, a gift from Lam Research, and the UIUC-ZJU grant.

## REFERENCES

- (1) Li, X.; Bohn, P. W. Metal-Assisted Chemical Etching in HF/  $H_2O_2$  Produces Porous Silicon. *Appl. Phys. Lett.* **2000**, 77, 2572.

- (2) Li, X. Metal Assisted Chemical Etching for High Aspect Ratio Nanostructures: a Review of Characteristics and Applications in Photovoltaics. *Curr. Opin. Solid State Mater. Sci.* **2012**, *16*, 71–81.

- (3) Huang, Z.; Geyer, N.; Werner, P.; de Boor, J.; Gösele, U. Metal-Assisted Chemical Etching of Silicon: A Review. *Adv. Mater.* **2010**, 23, 285–308.

- (4) Ranganathan, N.; Lee, D. Y.; Youhe, L.; Lo, G.-Q.; Prasad, K.; Pey, K. L. Influence of Bosch Etch Process on Electrical Isolation of TSV Structures. *IEEE Trans. Compon., Packag., Manuf. Technol.* **2011**, 1, 1497–1507.

- (5) Um, H.-D.; Kim, N.; Lee, K.; Hwang, I.; Hoon Seo, J.; Yu, Y. J.; Duane, P.; Wober, M.; Seo, K. Versatile control of metal-assisted chemical etching for vertical silicon microwire arrays and their photovoltaic applications. *Sci. Rep.* **2015**, *5*, 11277.

- (6) Kim, J. D.; Kim, M.; Kong, L.; Mohseni, P. K.; Ranganathan, S.; Pachamuthu, J.; Chim, W. K.; Chiam, S. Y.; Coleman, J. J.; Li, X. Self-Anchored Catalyst Interface Enables Ordered Via Array Formation from Sub-micron to millimeter Scale for Poly-and Single-Crystalline Silicon. ACS Appl. Mater. Interfaces 2018, 10, 9116–9122.

- (7) Li, L.; Liu, Y.; Zhao, X.; Lin, Z.; Wong, C.-P. Uniform Vertical Trench Etching on Silicon with High Aspect Ratio by Metal-Assisted Chemical Etching Using Nanoporous Catalysts. *ACS Appl. Mater. Interfaces* **2013**, *6*, 575–584.

- (8) Kim, M.; Yi, S.; Kim, J. D.; Yin, X.; Li, J.; Bong, J.; Liu, D.; Liu, S.-C.; Kvit, A.; Zhou, W.; Wang, X.; Yu, Z.; Ma, Z.; Li, X. Enhanced Performance of Ge Photodiodes via Monolithic Antireflection Texturing and  $\alpha$ -Ge Self-passivation by Inverse Metal-Assisted Chemical Etching. *ACS Nano* **2018**, *12*, 6748–6755.

- (9) Kim, M.; Huang, H.-C.; Kim, J. D.; Kim, J. D.; Chabak, K. D.; Kalapala, A. R. K.; Zhou, W.; Li, X. Nanoscale Groove Textured  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> by Room Temperature Inverse Metal-Assisted Chemical Etching and Photodiodes with Enhanced Responsitiy. *Appl. Phys. Lett.* **2018**, *113*, 222104.

- (10) Kong, L.; Song, Y.; Kim, J. D.; Yu, L.; Wasserman, D.; Chim, W. K.; Chiam, S. Y.; Li, X. Damage-Free Smooth-Sidewall InGaAs Nanopillar Array by Metal-Assisted Chemical Etching. *ACS Nano* **2017**, *11*, 10193–10205.

- (11) Mohseni, P. K.; Hyun Kim, S.; Zhao, X.; Balasundaram, K.; Dong Kim, J.; Pan, L.; Rogers, J. A.; Coleman, J. J.; Li, X. GaAs Pillar Array-Based Light Emitting Diodes Fabricated by Metal-Assisted Chemical Etching. *J. Appl. Phys.* **2013**, *114*, 064909.

- (12) Oh, J.; Yuan, H.-C.; Branz, H. M. An 18.2%-Efficient Black-Silicon Solar Cell Achieved through Control of Carrier Recombination in Nanostructures. *Nat. Nanotechnol.* **2012**, *7*, 743–748.

- (13) Stewart, M. P.; Buriak, J. M. Chemical and Biological Applications of Porous Silicon Technology. *Adv. Mater.* **2000**, *12*, 859–869.

- (14) Chang, S.-W.; Oh, J.; Boles, S. T.; Thompson, C. V. Fabrication of Silicon Nanopillar-Based Nanocapacitor Arrays. *Appl. Phys. Lett.* **2010**, *96*, 153108.

- (15) Zhang, T.; Wu, S.; Xu, J.; Zheng, R.; Cheng, G. High Thermoelectric Figure-of-Merits from Large-Area Porous Silicon Nanowire Arrays. *Nano Enegy* **2015**, *13*, 433–441.

- (16) Song, Y.; Mohseni, P. K.; Kim, S. H.; Shin, J. C.; Ishihara, T.; Adesida, I.; Li, X. Ultra-High Aspect Ratio InP Junctionless FinFETs by a Novel Wet Etching Method. *IEEE Electron Device Lett.* **2016**, 37, 970–973.

- (17) Geyer, N.; Fuhrmann, B.; Huang, Z.; de Boor, J.; Leipner, H. S.; Werner, P. Model for the Mass Transport during Metal-Assisted Chemical Etching with Contiguous Metal Films as Catalysts. *J. Phys. Chem. C* 2012, *116*, 13446–13451.

- (18) Lai, C. Q.; Cheng, He.; Choi, W. K.; Thompson, C. V. Mechanics of Catalyst Motion during Metal Assisted Chemical Etching of Silicon. *J. Phys. Chem. C* **2013**, *117*, 20802–20809.

- (19) Hildreth, O. J.; Rykaczewski, K.; Fedorov, A. G.; Wong, C. P. A DLVO Model for Catalyst Motion in Metal-Assisted Chemical Etching Based Upon Controlled Out-of-Plane Rotational Etching and Force-Displacement Measurements. *Nanoscale* **2013**, *5*, 961–970.

- (20) Rykaczewski, K.; Hildreth, O. J.; Wong, C. P.; Fedorov, A. G.; Scott, J. H. J. Guided Three-Dimensional Catalyst Folding During Metal-Assisted Chemical Etching of Silicon. *Nano Lett.* **2011**, *11*, 2369–2374.

- (21) Lai, R. A.; Hymel, T. M.; Narasimhan, V. K.; Cui, Y. Schottky Barrier Catalysis Mechanism in Metal-Assisted Chemical Etching of Silicon. *ACS Appl. Mater. Interfaces* **2016**, *8*, 8875–8879.

- (22) Tavendale, A. J.; Pearton, S. J. Deep Level, Quenched-in Defects in Silicon Doped with Gold, Silver, Iron, Copper or Nickel. *J. Phys. C: Solid State Phys.* **1983**, *16*, 1665–1673.

- (23) Kim, J.; Lee, D. H.; Kim, J. H.; Choi, S.-H. Graphene-Assisted Chemical Etching of Silicon Using Anodic Aluminum Oxides as Patterning Templates. ACS Appl. Mater. Interfaces 2015, 7, 24242–24246.

- (24) Tang, T. E.; Che-Chia Wei, C.-C.; Haken, R. A.; Holloway, T. C.; Hite, L. R.; Blake, T. G. W. Titanium Nitride Local Interconnect Technology for VL. *IEEE Trans. Electron Devices* **1987**, 34, 682–688.

- (25) Lee, Y.; George, S. M. Thermal Atomic Layer Etching of Titanium Nitride Using Sequantial, Self-Limiting Reactions: Oxidation to TiO<sub>2</sub> and Fluorination to Volatile TiF<sub>4</sub>. *Chem. Mater.* **2017**, 29, 8202–8210.

- (26) Williams, K. R.; Gupta, K.; Wasilik, M. Etch rates for micromachining processing Part II. *J. Microelectromech. Syst.* **2003**, 12, 761–778.

- (27) Mazza, F.; Trassatti, S. Tungsten, Titanium, and Tantalum Carbides and Titanium Nitrides as Electrodes in Redox Systems. *J. Electrochem. Soc.* **1963**, *110*, 682.

- (28) Lima, L. P. B.; Diniz, J. A.; Doi, I.; Godoy Fo, J. Titanium Nitride as Electrode for MOS Technology and Schottky Diode: Alternative Extraction Method of Titanium Nitride Work Function. *Microelectron. Eng.* **2012**, 92, 86–90.

- (29) Fouilland, L.; Imhoff, L.; Bouteville, A.; Benayoun, S.; Remy, J. C.; Perrière, J.; Morcrette, M. Composition and tribological characterization of chemically vapour-deposited TiN layer. *Surf. Coat. Technol.* **1998**, *100*–*101*, 146–148.

- (30) Hildreth, O. J.; Schmidt, D. R. Vapor-phase Metal-Assisted Chemical Etching of Silicon. *Adv. Funct. Mater.* **2014**, *24*, 3827–3833.

- (31) Kim, S. H.; Mohseni, P. K.; Song, Y.; Ishihara, T.; Li, X. Inverse Metal-Assisted Chemical Etching of InP Produces Smooth High Aspect Ratio Nanostructures. *Nano Lett.* **2015**, *15*, 641–648.

- (32) Cussler, E. L. Diffusion: Mass Transfer in Fluid Systems; Cambridge University Press, 2009.

- (33) Dill, K. A.; Bromberg, S. Molecular Driving Forces: Statistical Thermodynamics in Chemistry and Biology, Macromolecular Chemistry and Physics Garland Science; Taylor & Francis, 2013.

- (34) Kim, J. D.; Mohseni, P. K.; Balasundaram, K.; Ranganathan, S.; Pachamuthu, J.; Coleman, J. J.; Li, X. Scaling the Aspect Ratio of Nanoscale Closely Packed Silicon Vias by MacEtch: Kinetics of Carrier Generation and Mass Transport. *Adv. Funct. Mater.* **2017**, 27, 1605614.

- (35) Zuo, Z.; Cui, G.; Shi, Y.; Liu, Y.; Ji, G. Gold-Thickness-Dependent Schottky Barrier Height for Charge Transfer in Metal-Assisted Chemical Etching of Silicon. *Nanoscale Res. Lett.* **2013**, *8*, 193

- (36) Vitale, S. A.; Kedzierski, J.; Healey, P.; Wyatt, P. W.; Keast, C. L. Work-Function-Tuned TiN Metal Gate FDSOI Transistors for Subthreshold Operation. *IEEE Trans. Electron Devices* **2011**, 58, 419–426

- (37) Balasundaram, K.; Sadhu, J. S.; Shin, J. C.; Azeredo, B.; Chanda, D.; Malik, M.; Hsu, K.; Rogers, J. A.; Ferreira, P.; Sinha, S.; Li, X. Porosity control in metal-assisted chemical etching of degenerately doped silicon nanowires. *Nanotechnology* **2012**, *23*, 305304.

- (38) Geyer, N.; Wollschläger, N.; Fuhrmann, B.; Tonkikh, A.; Berger, A.; Werner, P.; Jungmann, M.; Krause-Rehberg, R.; Leipner, H. S. Influence of the doping level on the porosity of silicon nanowires prepared by metal-assisted chemical etching. *Nanotechnology* **2015**, *26*, 245301.

- (39) Liu, R.; Zhao, X.; Roberts, C.; Yu, L.; Mohseni, P. K.; Li, X.; Podolskiy, V.; Wasserman, D. Enhanced Optical Transmission through MacEtch-Fabricated Buried Metal Gratings. *Adv. Mater.* **2016**, 28, 1441–1448.

- (40) Li, W.; Guler, U.; Kinsey, N.; Naik, G. V.; Naik, A.; Boltasseva, A.; Guan, J.; Shalaev, V. M.; Kildishev, A. V. Refractory plasmonics with titanium nitride: broadband metamaterial absorber. *Adv. Mater.* **2014**, *26*, 7959–7965.